UART (Universal Asynchronous Transmitter Receiver), questo è il protocollo più comune usato per la comunicazione seriale full-duplex. È un singolo chip LSI (large scale integration) progettato per eseguire la comunicazione asincrona. Questo dispositivo invia e riceve dati da un sistema a un altro sistema.

In questo tutorial, imparerete le basi della comunicazione UART, e il funzionamento dell’UART.

Che cos’è UART?

“UART” sta per Universal Asynchronous receiver-transmitter. È una periferica hardware presente all’interno di un microcontrollore. La funzione di UART è di convertire i dati in entrata e in uscita nel flusso binario seriale. Un dato seriale a 8 bit ricevuto dalla periferica viene convertito in forma parallela usando la conversione da seriale a parallela e i dati paralleli ricevuti dalla CPU vengono convertiti usando la conversione da seriale a parallela. Questi dati sono presenti in forma modulante e vengono trasmessi ad un baud rate definito.

Perché si usa UART?

Protocolli come SPI (interfaccia periferica seriale) e USB (Universal Serial Bus) sono usati per la comunicazione veloce. Quando il trasferimento di dati ad alta velocità non è richiesto, si usa UART. È un dispositivo di comunicazione economico con un singolo trasmettitore/ricevitore. Richiede un solo filo per la trasmissione dei dati e un altro filo per la ricezione.

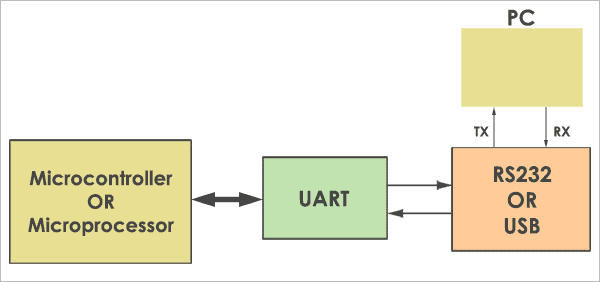

Interfaccia UART

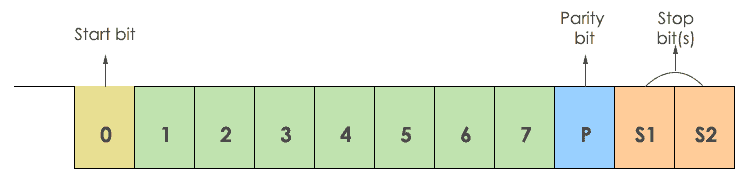

Si può interfacciare con un PC (personal computer) usando un convertitore RS232-TTL o un convertitore USB-TTL. La cosa comune tra RS232 e UART è che entrambi non richiedono un clock per trasmettere e ricevere dati. Il frame Uart consiste di 1 bit di inizio, 1 o 2 bit di stop e un bit di parità per il trasferimento di dati seriali.

Schema a blocchi

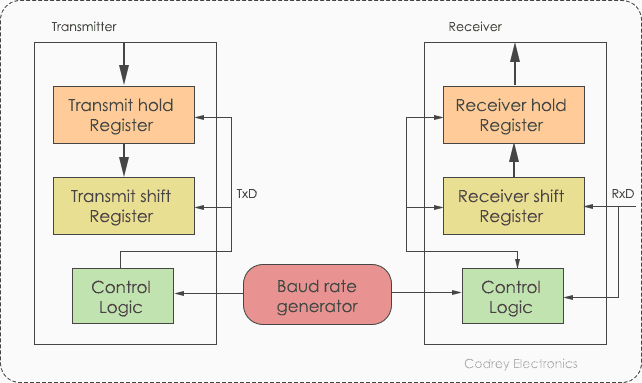

L’UART consiste dei seguenti componenti principali. Sono il trasmettitore e il ricevitore. Il trasmettitore consiste nel Transmit hold register, Transmit shift register, e la logica di controllo. Allo stesso modo, il ricevitore consiste in un registro hold di ricezione, uno shift register di ricezione e una logica di controllo. In comune, sia il trasmettitore che il ricevitore sono dotati di un generatore di baud rate.

Schema a blocchi UART

Il generatore di baud rate genera la velocità alla quale il trasmettitore e il ricevitore devono inviare/ricevere i dati. Il Transmit hold register contiene il byte di dati da trasmettere. Lo shift register di trasmissione e lo shift register di ricezione spostano i bit a sinistra o a destra fino a quando un byte di dati viene inviato/ricevuto.

In aggiunta a questi, una logica di controllo di lettura o scrittura è fornita per dire quando leggere/scrivere. Il generatore di baud rate genera velocità che vanno da 110 bps (bit per secondo) a 230400. Per lo più, i microcontrollori sono dotati di baud rate più alti come 115200 e 57600 per un trasferimento dati più veloce. Dispositivi come GPS e GSM usano baud rate più lenti, 4800 e 9600.

Come funziona UART?

Per conoscere il funzionamento di UART, è necessario capire la funzionalità di base della comunicazione seriale. In breve, il trasmettitore e il ricevitore usano il bit di inizio, il bit di stop e i parametri di temporizzazione per sincronizzarsi tra loro. I dati originali sono in forma parallela. Per esempio, abbiamo dati a 4 bit, per convertirli in forma seriale, abbiamo bisogno di un convertitore da parallelo a seriale. Generalmente, per progettare i convertitori si usano flip-flop D o latches.

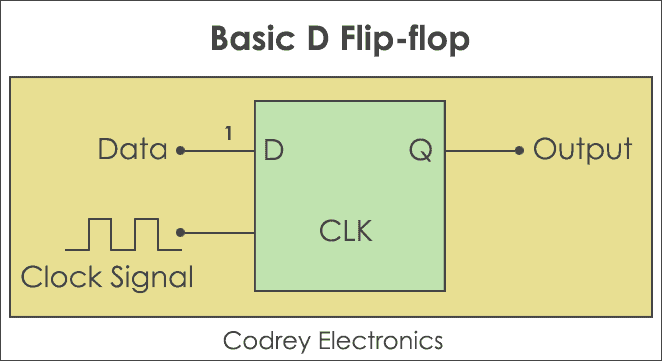

Funzionamento di D – Flip-flop

Basic D Flip-Flop

D flip-flop conosciuto anche come Data flip-flop sposta un bit dal lato ingresso al lato uscita se e solo, quando il clock cambia la transizione da uno stato alto a uno stato basso o da uno stato basso a uno stato alto. Allo stesso modo, se volete trasferire quattro bit di dati avete bisogno di 4 flip-flop.

Nota: Qui,

‘D’ rappresenta i dati di ingresso.

‘CLK’ indica gli impulsi di clock.

‘Q’ denota i dati di uscita. Ora, progettiamo un convertitore da parallelo a seriale e da seriale a parallelo.

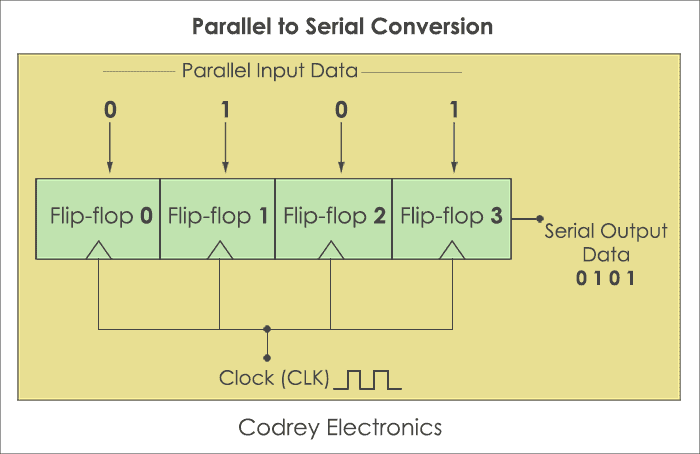

Conversione da parallelo a seriale

Conversione da parallelo a seriale

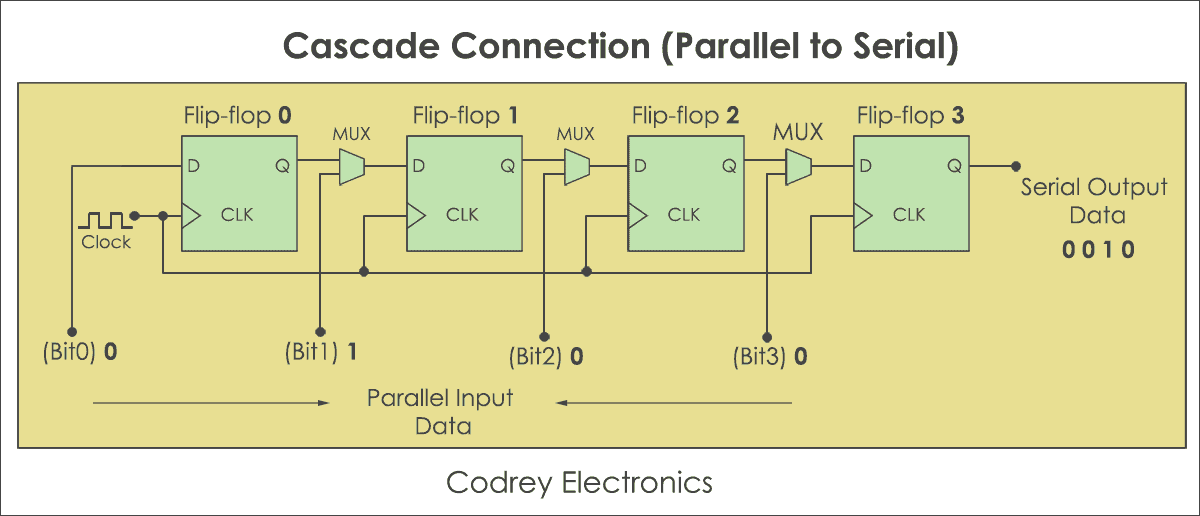

Connessione a cascata – Parallela a Seriale

Step#1:

Prendere 4 flip-flop. Il numero di flip-flop è equivalente al numero di bit da trasmettere. Allo stesso modo, mettete dei multiplexer davanti ad ogni flip-flop, ma escludendo il primo. Un multiplexer è posto per combinare i dati e convertirli in bit seriali. Ha due ingressi, un bit di dati paralleli e un altro dal flip-flop precedente.

Step#2:

Ora, carica i dati alla volta nei flip-flop D. Tirerà i dati paralleli e sposterà l’ultimo bit dell’ultimo flip-flop (quattro), e poi il terzo bit, il secondo bit, e infine il primo bit. Ora, per riconvertire i dati paralleli in forma seriale viene usato un convertitore da seriale a parallelo.

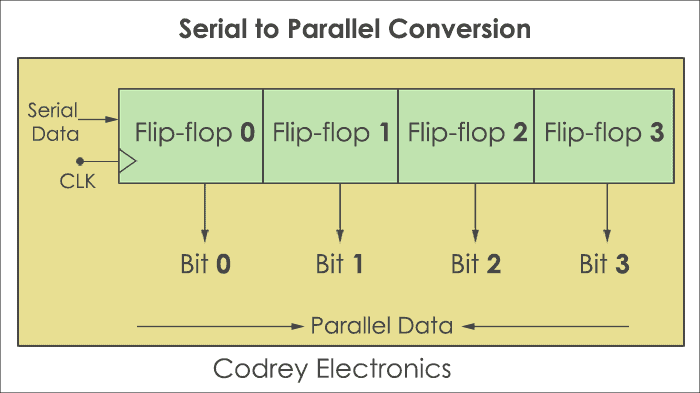

Conversione da seriale a parallela

Conversione da seriale a parallela

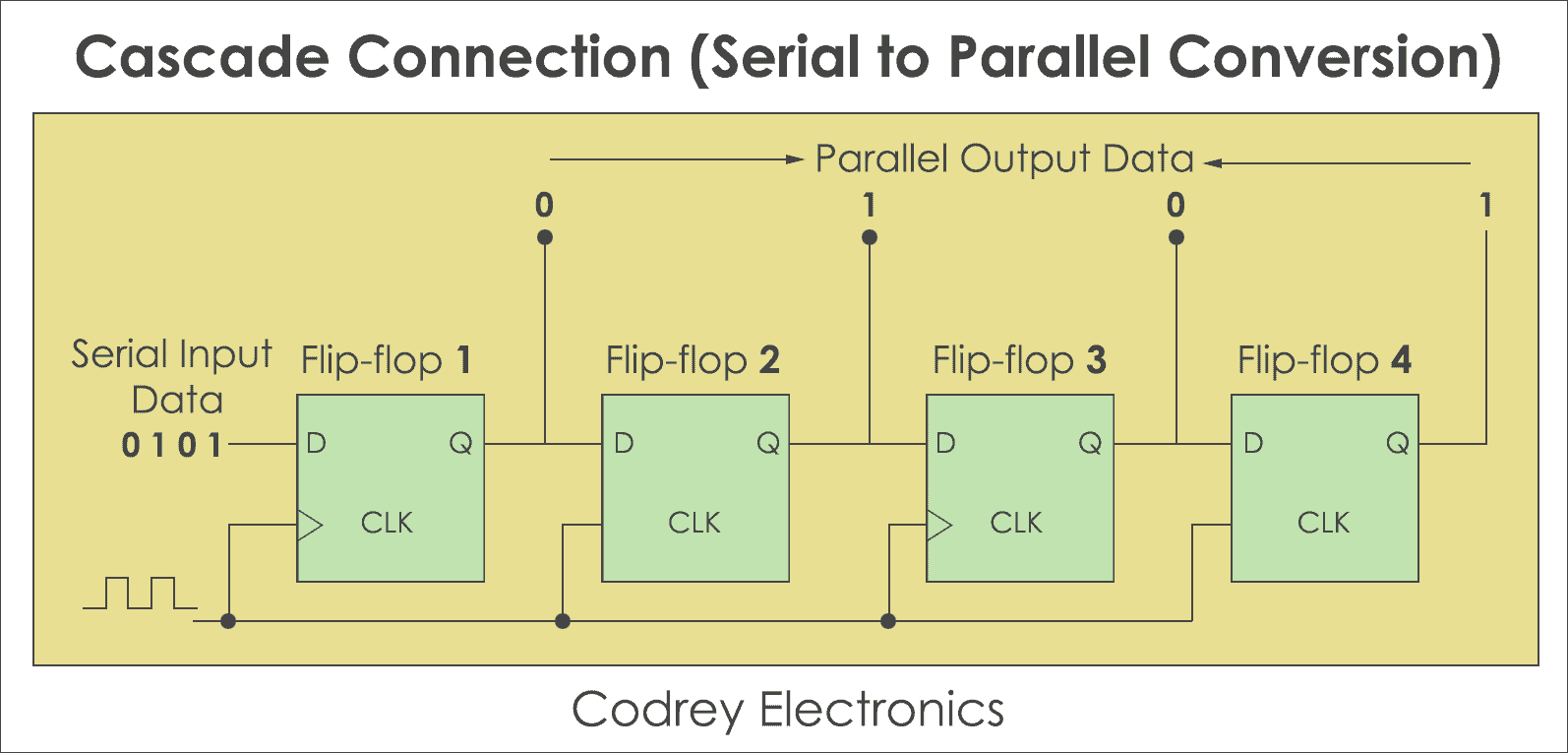

Connessione a cascata – Conversione da seriale a parallela

Step#1:

Prendere 4 Flip-flop. Il numero di flip-flop è uguale al numero di bit da trasmettere.

Step#2:

Inzialmente, disabilita il bus parallelo. Non abilitare fino a quando tutti i bit sono caricati. Memorizzate i dati all’ingresso del primo flip-flop. Ora rendete alto il clock, questo sposterà il bit meno significativo all’ingresso del secondo flip-flop e all’uscita del primo. Allo stesso modo, spostate tutti i bit uno per uno rendendo alto l’impulso di clock. Il convertitore è in stato di attesa fino a quando tutti i bit sono trasferiti all’uscita.

Step#3:

Ora ogni flip-flop contiene un bit di dati seriali. Nel frattempo tutti i bit sono trasferiti all’uscita del flip-flop, abilita il bus. Questo farà sì che il convertitore invii tutti i bit alla volta.

Formato del protocollo

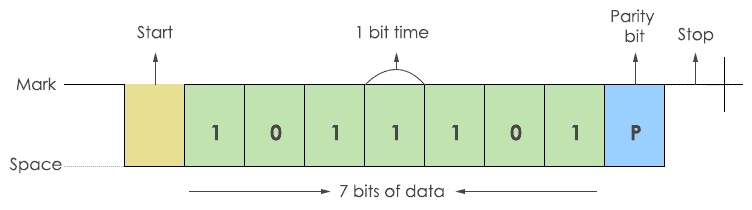

L’UART inizia la comunicazione con un bit di inizio ‘0’. Il bit di inizio inizia il trasferimento dei dati seriali e il bit di stop termina la transazione dei dati.

Formato del protocollo

È anche dotato di un bit di parità (pari o dispari). Il bit di parità pari è rappresentato da ‘0’ (numero pari di 1) e il bit di parità dispari è rappresentato da ‘1’ (numero dispari di 1).

Trasmissione

La trasmissione dei dati è fatta usando una singola linea di trasmissione (TxD). Qui ‘0’ è considerato come spazio e ‘1’ è conosciuto come stato di mark.

Transmission Frame

Il trasmettitore invia un singolo bit alla volta. Dopo aver inviato un bit, viene inviato il bit successivo. In questo modo, tutti i bit di dati sono inviati al ricevitore con un baud rate predefinito. Ci sarà un certo ritardo nella trasmissione di ogni bit. Per esempio, per inviare un byte di dati a 9600 baud rate, ogni bit viene inviato con 108 µsec di ritardo. I dati vengono aggiunti con un bit di parità. Così, 10 bit di dati sono richiesti per inviare 7 bit di dati.

Nota: In trasmissione, sempre LSB (Least Significant Bit) è inviato per primo.

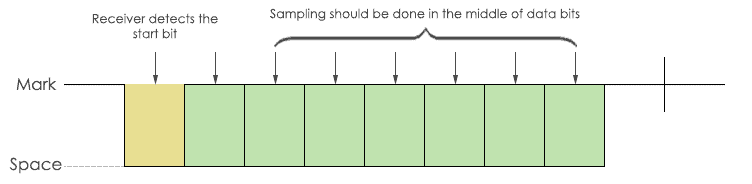

Reception

Durante la ricezione, la linea RxD (Receiver) è usata per ricevere i dati.

Receive Frame

Esempio di interfacciamento UART

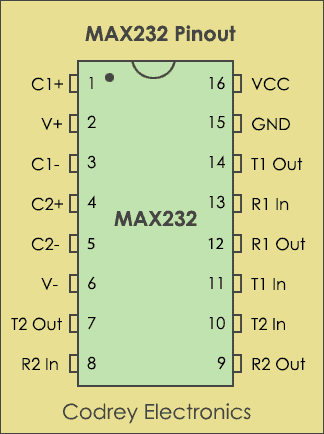

Questo esempio dimostra l’interfacciamento di ESP8266 UART con MAX232. Ma, prima di saltare nei dettagli dell’interfacciamento, lasciatemi condividere i dettagli dei pin del driver Max232.

MAX232 Pinout

MAX232 IC è alimentato da 5V che include un generatore di tensione capacitivo per guidare tensioni di livello 232. Viene fornito con due trasmettitori chiamati anche driver (TIN, TOUT) e ricevitori (RIN e ROUT).

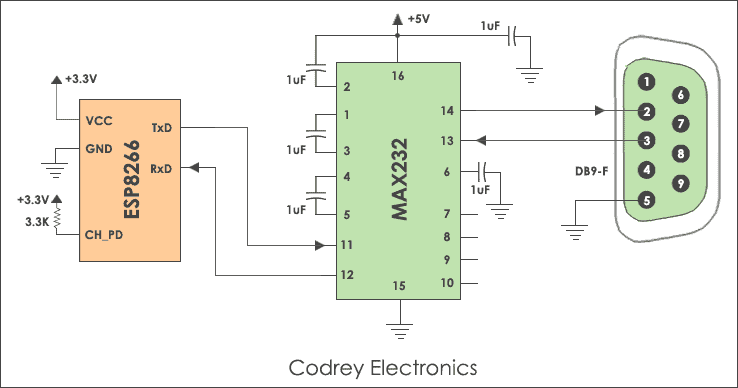

Qui ho usato ESP8266 (microcontrollore a 32 bit) che ha una UART integrata. La comunicazione può essere fatta con ESP8266 usando i comandi AT tramite RS232 al convertitore di livello TTL (MAX232). La figura sottostante mostra la connessione di ESP8266 con il PC (personal computer).

ESP8266 che si interfaccia con UART

Richiedendo comandi AT validi attraverso il PC il chip Wi-Fi risponderà con una conferma. Non voglio approfondire l’ESP8266 e sarà spiegato nei futuri tutorial.

Questi sono i passi per implementare la comunicazione seriale con il PC.

- Collegare il trasmettitore (TX) di ESP8266 al ricevitore (TX) del convertitore da RS232 a livello TTL (MAX232) e RX del PC.

- Collegare il ricevitore (RX) di ESP8266 al TX del PC e RX del convertitore TTL.

Comandi di ESP8266

| Comando AT (Inviato dal PC) | Risposta di ESP8266 (ricevuta dal PC) |

|---|---|

| AT<CR><LF> | OK<CR><LF> |

| AT+CIPMUX=1 | OK<CR><LF> | AT+CIPSERVER=1,23<CR><LF> | OK<CR><LF> |

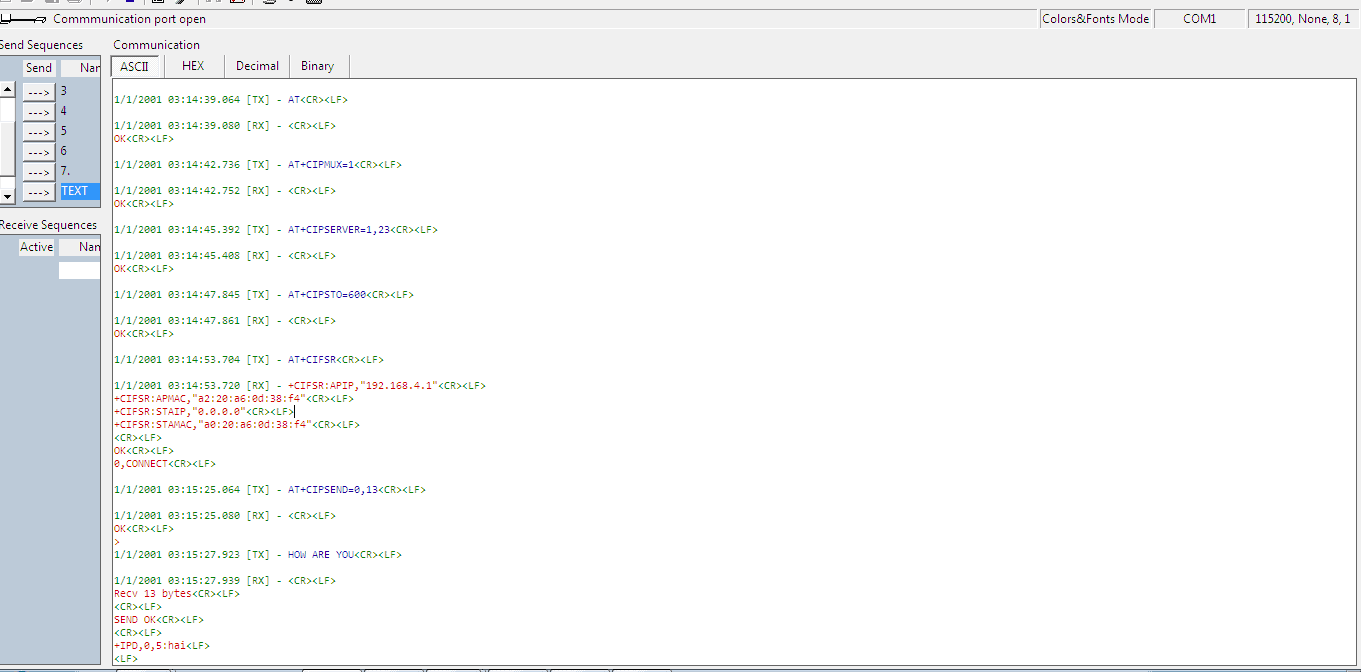

Lo screenshot seguente mostra la risposta data dal modulo ESP8266.

Comandi ESP8266 – Programma Docklight

UART vs USART

USART è la forma base di UART. Tecnicamente, non sono la stessa cosa. Ma la definizione è la stessa per entrambe. Sono periferiche per microcontrollori che convertono dati paralleli in bit seriali e viceversa.

La differenza principale tra UART e USART è che UART supporta solo la comunicazione asincrona, mentre USART supporta la comunicazione sincrona e asincrona. Per una facile comprensione, ecco il confronto tra USART e UART.

| UART | USART |

|---|---|

| Il clock è generato internamente dal microcontrollore. | Il dispositivo di invio genererà il clock. |

| La velocità dei dati è lenta. | La velocità dei dati è più alta a causa del clock esterno. |

| Protocollo Standalone | Supporta più protocolli come LIN, RS-485, IrDA, Smart Card ecc. |

| Il baud rate deve essere conosciuto prima della trasmissione. | Non è necessario conoscere il baud rate prima. |

| Adatto per comunicazioni a bassa velocità | Adatto per comunicazioni ad alta velocità. |

| Riduzione dell’impatto energetico. | Gestisce la comunicazione seriale durante l’alto consumo energetico |

RS232 e UART

I livelli logici rappresentano i livelli di tensione operativa che un dispositivo può sopportare per funzionare in una zona sicura. Ecco i livelli di tensione per RS232 e TTL.

Logica RS232:

Livelli di tensione RS232

| Livello logico | Gamma di tensione |

|---|---|

| L’uscita Logic High o OFF | -5V a -15V |

| Uscita logica bassa o ON | +5V a +15V |

| Ingresso logico alto o OFF | -3V a -15V |

| Ingresso logico basso o ON | +3V a +15V |

Nella maggior parte dei casi i livelli RS232 vanno da -12V a +12V. Per esempio, un valore ASCII per un carattere “A” in RS232 è 65 e 41 in esadecimale. Quindi, in un formato binario a 8 bit, è 0100 0001. Qui mostra la rappresentazione dei livelli logici RS232 per ASCII ‘A’.

Segnale RS232 per ASCII Lettera A

L/CMOS Logic:

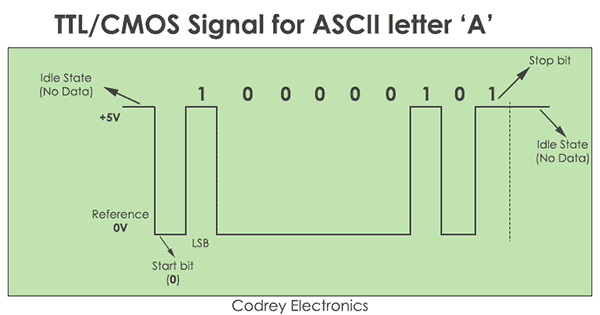

L’UART lavora su logica TTL.

Segnale TTL CMOS per ASCI Lettera A

- Inzialmente, la linea seriale è nello stato inattivo comunemente chiamato stato Mark (Logico 1). Ora, la trasmissione dei dati inizia con un bit di inizio (0 logico).

- In seguito, otto bit di dati sono inviati sulla linea seriale uno dopo l’altro con LSB (Least significant bit) per primo.

- Dopo che l’intera trasmissione è finita, si incontra un bit di stop (1 logico).

Avantaggi

Il vantaggio di UART è che supporta la comunicazione full-duplex usando due fili. Inoltre, non richiede un clock esterno per la comunicazione dei dati. Supporta il controllo degli errori usando un bit di parità e la lunghezza dei dati può essere cambiata facilmente.

Svantaggi

Il principale svantaggio di UART è che non supporta la configurazione multi-slave o multi-master. Inoltre, la dimensione del pacchetto dati è limitata a 9 bit. L’UART non è adatto alla comunicazione seriale pesante durante il consumo di alta energia.

Applicazioni

- La porta di debug seriale usa il driver UART per stampare i dati provenienti dal mondo esterno.

- Possiamo usarla per inviare e ricevere comandi da e verso i dispositivi embedded.

- La comunicazione in GPS, modem GSM/GPRS, chip Wi-Fi, ecc funziona con UART.

- Utilizzato in accesso Mainframe per collegare diversi computer.